# MOS INTEGRATED CIRCUIT

$\mu$ **PD17120**

# SMALL GENERAL-PURPOSE 4 BIT SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD17120 is a 4-bit single-chip microcontroller containing timer, a power-on/power-down reset circuit, and a serial interface.

For the CPU, the  $\mu$ PD17120 employs a 17K architecture using general registers. The new architecture allows operations to be performed directly on data memory, without involving accumulators as conventionally done. In addition, each instruction is 16 bits (one word) long, allowing programming to be done efficiently.

The  $\mu$ PD17P132, a one-time PROM product, is available for evaluation of the  $\mu$ PD17120 and for small-scale production.

The following user's manual completely describes the functions of the  $\mu$ PD17120. Be sure to read it before designing an application system.

$\mu$ PD17120 Sub-Series User's Manual: IEU-1367

#### **FEATURES**

• 17K architecture: General registers, 16-bit instructions

Program memory (ROM):

1.5K bytes (768 × 16 bits)

Data memory (RAM): 64 × 4 bits

• Instruction execution time: 8  $\mu$ s (when the microcontroller operates at 2 MHz with RC

oscillationNote)

External interrupt:

1 line (INT pin, with sensor input)

Timer function: 1 channel3-wire serial interface: 1 channel

Input/output pins:

19 pins (including one sensor input pin)

• Power-on/power-down reset function

• Supply voltage:  $V_{DD} = 2.7 \text{ to } 5.5 \text{ V}$

**Note** The capacitor for RC oscillation is contained in the  $\mu$ PD17120.

#### **APPLICATIONS**

Controlling electric appliances such as electric fans

The information in this document is subject to change without notice.

#### **ORDERING INFORMATION**

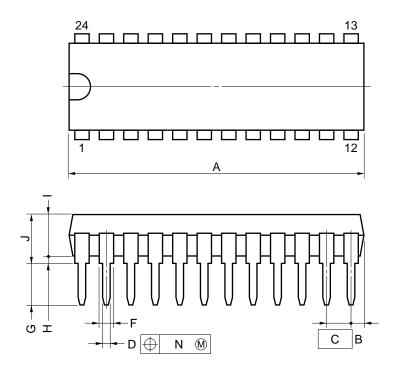

| Part number                                   | Package                             |

|-----------------------------------------------|-------------------------------------|

| μPD17120CS-×××                                | 24-pin plastic shrink DIP (300 mil) |

| $\mu$ PD17120GT- $\times\!\!\times\!\!\times$ | 24-pin plastic SOP (375 mil)        |

**Remark** ××× indicates the ROM code.

#### **CHARACTERISTICS**

| Item                              | Description                                                                                                                                      |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ROM capacity                      | 1.5K bytes (768 × 16 bits)                                                                                                                       |  |  |  |  |

| RAM capacity                      | $64 \times 4$ bits (The stack is separated from memory.)                                                                                         |  |  |  |  |

| Stack                             | 5 address stacks, 1 interrupt stack                                                                                                              |  |  |  |  |

| Number of input/output ports      | 19   • 18 input/output ports • 1 input port for sensing an interrupt (INT pinNote)                                                               |  |  |  |  |

|                                   | 1 channel (8-bit timer)                                                                                                                          |  |  |  |  |

| Timer                             | 1 channel (3-wire type)                                                                                                                          |  |  |  |  |

| Serial interface Interrupt        | <ul> <li>1 external interrupt         (INT)</li></ul>                                                                                            |  |  |  |  |

| Execution time of an instruction  | 8 $\mu$ s (when operating at 2 MHz with RC oscillation)                                                                                          |  |  |  |  |

| Standby function                  | STOP, HALT                                                                                                                                       |  |  |  |  |

| Power-on/power-down reset circuit | Built-in (Can be used in an application circuit where V <sub>DD</sub> is 5 V ±10 %)                                                              |  |  |  |  |

| Operating power voltage           | <ul> <li>V<sub>DD</sub> = 2.7 to 5.5 V</li> <li>V<sub>DD</sub> = 4.5 to 5.5 V (when the power-on/power-down reset functions are used)</li> </ul> |  |  |  |  |

| Package                           | 24-pin plastic shrink DIP (300 mil)     24-pin plastic SOP (375 mil)                                                                             |  |  |  |  |

| One-time PROM product             | μPD17P132                                                                                                                                        |  |  |  |  |

- ★ Note The INT pin can be used as an input pin (sensor input) when the external interrupt function is not used. The status of the pin is read with the INT flag of the control register, not with the port register.

- ★ Caution Although a PROM product is highly compatible with a masked ROM product in respect of functions, they differ in internal ROM circuits and part of electrical characteristics. Before changing the PROM product to the masked ROM product in an application system, evaluate the system carefully using the masked ROM product.

# **CONTENTS**

| 1.  | PIN CONFIGURATION (TOP VIEW) |                                        |    |  |  |  |  |  |

|-----|------------------------------|----------------------------------------|----|--|--|--|--|--|

| 2.  | . BLOCK DIAGRAM              |                                        |    |  |  |  |  |  |

| 3.  | PINS                         |                                        | 8  |  |  |  |  |  |

|     | 3.1                          | PIN FUNCTIONS                          | 8  |  |  |  |  |  |

|     | 3.2                          | PIN EQUIVALENT CIRCUIT                 | g  |  |  |  |  |  |

|     | 3.3                          | HANDLING UNUSED PINS                   | 10 |  |  |  |  |  |

|     | 3.4                          | NOTES ON USE OF THE RESET AND INT PINS | 11 |  |  |  |  |  |

| 4.  | PROG                         | RAM MEMORY (ROM)                       | 12 |  |  |  |  |  |

|     | 4.1                          | PROGRAM MEMORY ORGANIZATION            | 12 |  |  |  |  |  |

| 5.  | PROG                         | RAM COUNTER (PC)                       | 13 |  |  |  |  |  |

|     | 5.1                          | PROGRAM COUNTER CONFIGURATION          | 13 |  |  |  |  |  |

|     | 5.2                          | PROGRAM COUNTER OPERATION              | 13 |  |  |  |  |  |

|     | 5.3                          | NOTES ON USING THE PROGRAM COUNTER     | 13 |  |  |  |  |  |

| 6.  | STAC                         | Κ                                      | 14 |  |  |  |  |  |

| 7.  | DATA                         | MEMORY (RAM)                           | 15 |  |  |  |  |  |

|     | 7.1                          | DATA MEMORY ORGANIZATION               | 15 |  |  |  |  |  |

|     | 7.2                          | UNINSTALLED DATA MEMORY                | 15 |  |  |  |  |  |

| 8.  | GENE                         | RAL REGISTER (GR)                      | 16 |  |  |  |  |  |

|     | 8.1                          | GENERAL REGISTER POINTER (RP)          | 16 |  |  |  |  |  |

| 9.  | SYST                         | EM REGISTER (SYSREG)                   | 17 |  |  |  |  |  |

|     | 9.1                          | SYSTEM REGISTER CONFIGURATION          | 17 |  |  |  |  |  |

| 10. | REGIS                        | STER FILE (RF)                         | 19 |  |  |  |  |  |

|     | 10.1                         | REGISTER FILE CONFIGURATION            | 19 |  |  |  |  |  |

|     | 10.2                         | FUNCTIONS OF THE REGISTER FILE         | 20 |  |  |  |  |  |

| 11. | DATA                         | BUFFER (DBF)                           | 21 |  |  |  |  |  |

|     | 11.1                         | DATA BUFFER CONFIGURATION              | 21 |  |  |  |  |  |

|     | 11.2                         | FUNCTIONS OF THE DATA BUFFER           | 22 |  |  |  |  |  |

| 12. | ALU   | BLOCK                                                                                                | 23 |

|-----|-------|------------------------------------------------------------------------------------------------------|----|

|     | 12.1  | ALU BLOCK CONFIGURATION                                                                              | 23 |

| 13. | POR1  | S                                                                                                    | 25 |

|     | 13.1  | PORT 0A (P0A <sub>0</sub> , P0A <sub>1</sub> , P0A <sub>2</sub> , P0A <sub>3</sub> )                 | 25 |

|     | 13.2  | PORT 0B (P0B <sub>0</sub> , P0B <sub>1</sub> , P0B <sub>2</sub> , P0B <sub>3</sub> )                 | 25 |

|     | 13.3  | PORT 0C (P0C <sub>0</sub> , P0C <sub>1</sub> , P0C <sub>2</sub> , P0C <sub>3</sub> )                 | 25 |

|     | 13.4  | PORT 0D (P0D <sub>0</sub> /SCK, P0D <sub>1</sub> /SO, P0D <sub>2</sub> /SI, P0D <sub>3</sub> /TMOUT) | 26 |

|     | 13.5  | PORT 0E (P0E <sub>0</sub> , P0E <sub>1</sub> )                                                       | 27 |

|     | 13.6  | NOTES ON MANIPULATING PORT REGISTERS                                                                 | 28 |

| 14. | 8-BIT | TIMER COUNTER (TM)                                                                                   | 29 |

|     | 14.1  | CONFIGURATION OF 8-BIT TIMER COUNTER                                                                 | 29 |

|     | 14.2  | OUTPUTTING A TIMER SIGNAL                                                                            | 30 |

| 15. | SERI  | AL INTERFACE (SIO)                                                                                   | 31 |

|     | 15.1  | FUNCTIONS OF THE SERIAL INTERFACE                                                                    | 31 |

|     | 15.2  | 3-WIRE SERIAL INTERFACE OPERATION MODES                                                              | 33 |

| 16. | INTE  | RRUPT FUNCTIONS                                                                                      | 35 |

|     | 16.1  | INTERRUPT SOURCE TYPES AND VECTOR ADDRESSES                                                          | 35 |

|     | 16.2  | HARDWARE COMPONENTS OF THE INTERRUPT CONTROL CIRCUIT                                                 | 36 |

| 17. | STAN  | IDBY FUNCTION                                                                                        | 37 |

|     | 17.1  | OVERVIEW OF THE STANDBY FUNCTION                                                                     | 37 |

|     | 17.2  | HALT MODE                                                                                            | 38 |

|     | 17.3  | STOP MODE                                                                                            | 39 |

| 18. | RESE  | Т                                                                                                    | 40 |

|     | 18.1  | RESET FUNCTIONS                                                                                      | 40 |

|     | 18.2  | RESETTING                                                                                            | 41 |

|     | 18.3  | POWER-ON/POWER-DOWN RESET FUNCTION                                                                   | 42 |

| 19. | INST  | RUCTION SET                                                                                          | 47 |

|     | 19.1  | LEGEND                                                                                               | 47 |

|     | 19.2  | LIST OF THE INSTRUCTION SET                                                                          | 48 |

|     | 19.3  | ASSEMBLER (AS17K) BUILT-IN MACRO INSTRUCTIONS                                                        | 49 |

| 20. | ASSE  | MBLER RESERVED WORDS                                                                                 | 50 |

|     | 20.1  | MASK OPTION PSEUDO INSTRUCTIONS                                                                      | 50 |

|     | 20.2  | RESERVED SYMBOLS                                                                                     | 52 |

| 21. ELECTRICAL CHARACTERISTICS                          | 58 |

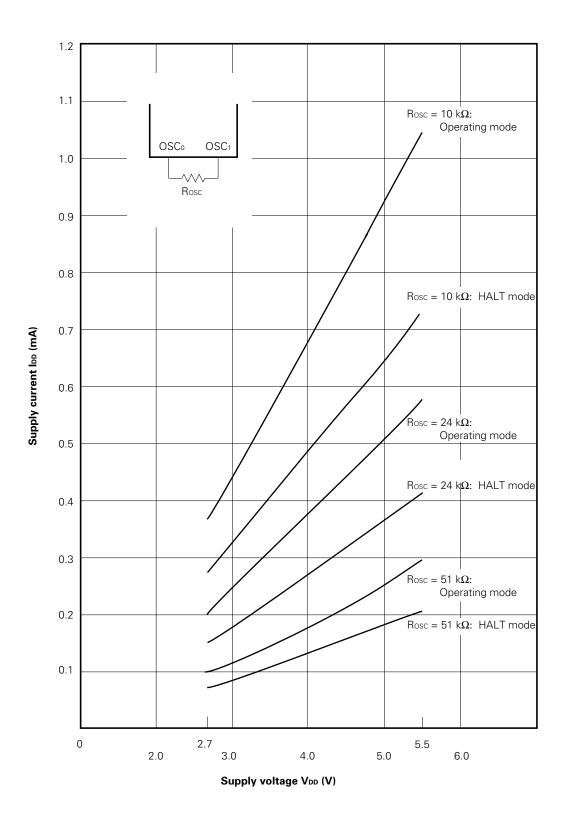

|---------------------------------------------------------|----|

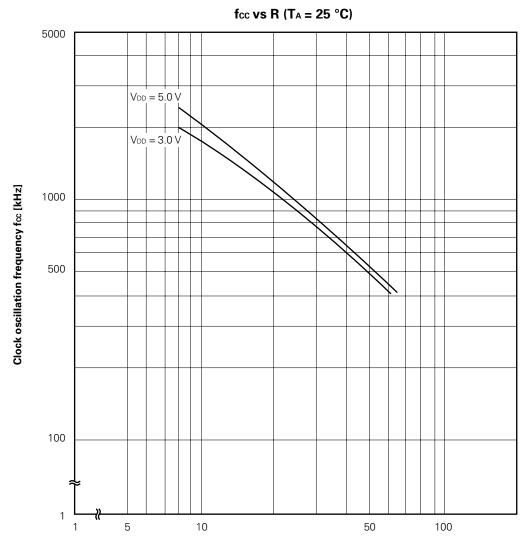

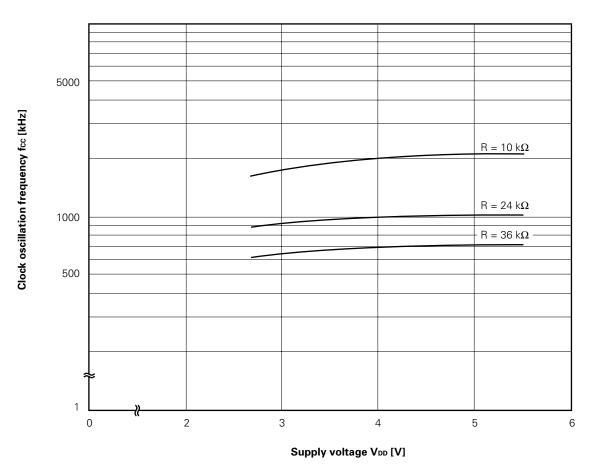

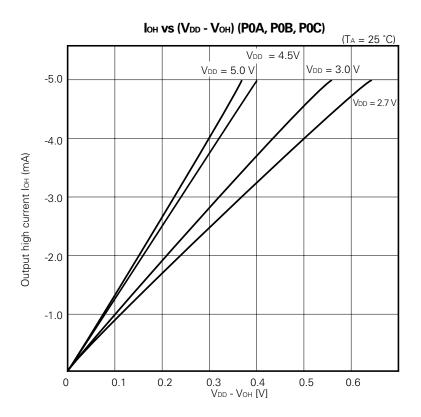

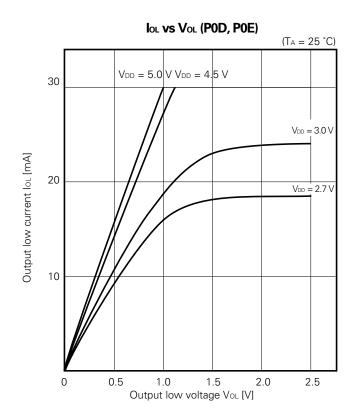

| 22. CHARACTERISTIC CURVES (FOR REFERENCE)               | 63 |

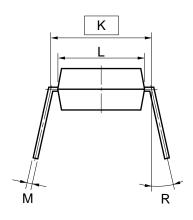

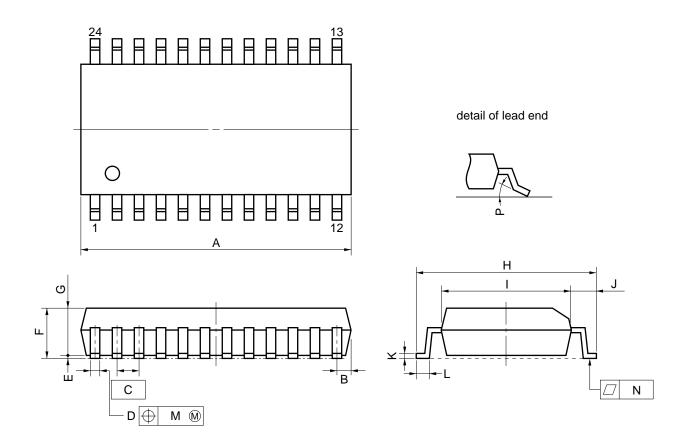

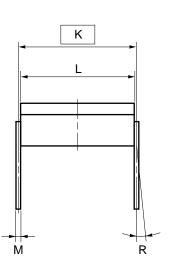

| 23. PACKAGE DRAWINGS                                    | 68 |

| 24. COMPARISON OF FUNCTIONS OF $\mu$ PD17120 SUB-SERIES | 72 |

| 25. RECOMMENDED SOLDERING CONDITIONS                    | 73 |

| APPENDIX DEVELOPMENT TOOLS                              | 74 |

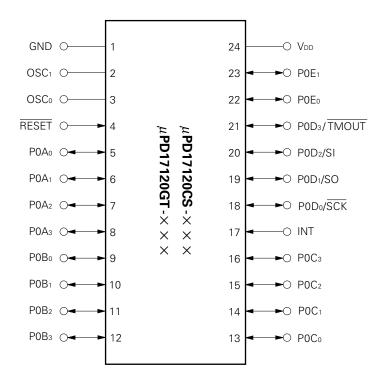

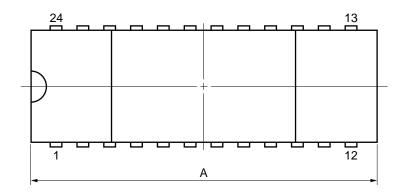

#### **PIN CONFIGURATION (TOP VIEW)**

24-pin plastic shrink DIP 24-pin plastic SOP

GND:

Ground

RESET: Reset input P0A<sub>0</sub>-P0A<sub>3</sub>: Port 0A TMOUT: P0B<sub>0</sub>-P0B<sub>3</sub>: Timer output Port 0B INT: External interrupt input P0C<sub>0</sub>-P0C<sub>3</sub>: Port 0C SI: Serial data input P0D<sub>0</sub>-P0D<sub>3</sub>: Port 0D SO: P0E<sub>0</sub>,P0E<sub>1</sub>: Serial data output Port 0E SCK: Serial clock input/output Power supply V<sub>DD</sub>:

OSC<sub>0</sub>,OSC<sub>1</sub>: System clock oscillation

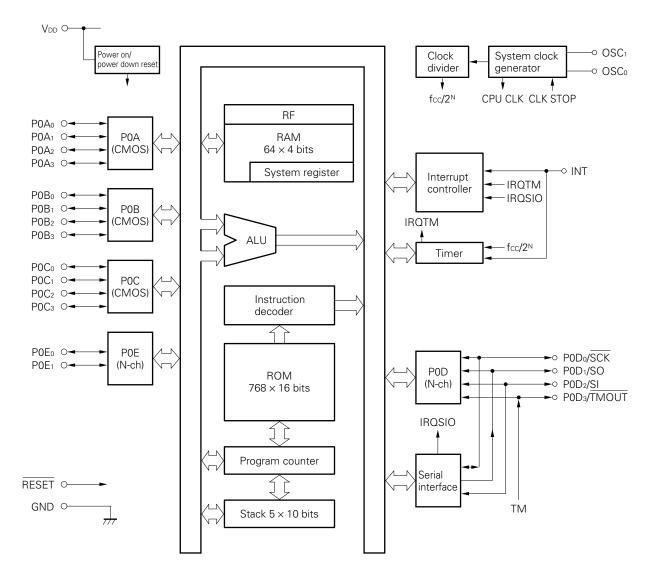

#### 2. BLOCK DIAGRAM

Remark The terms CMOS and N-ch in parentheses indicate the output form of the port.

CMOS: CMOS push-pull output

N-ch: N-channel open-drain output (Each pin can contain pull-up resistor as specified using a mask option.)

# 3. PINS

#### 3.1 PIN FUNCTIONS

| Pin No.  | Pin name                             | Function                                                                                                                                                                                                                                                                                               | Output          | After reset    |

|----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|

| 1        | GND                                  | Ground                                                                                                                                                                                                                                                                                                 | -               | _              |

| 2        | OSC <sub>1</sub><br>OSC <sub>0</sub> | For system clock oscillation Resistor is connected from OSC <sub>0</sub> to OSC <sub>1</sub> .                                                                                                                                                                                                         | -               | -              |

| 4        | RESET                                | Reset input pin  • Pull-up resistor incorporation specifiable by mask option                                                                                                                                                                                                                           | -               | Input          |

| 5 - 8    | P0A <sub>0</sub> - P0A <sub>3</sub>  | Port 0A  • 4-bit input/output port  • Input/output setting allowed in units of 1 bit                                                                                                                                                                                                                   | CMOS push-pull  | Input          |

| 9 - 12   | P0B <sub>0</sub> - P0B <sub>3</sub>  | Port 0B  • 4-bit input/output port  • Input/output setting allowed in units of 4 bits                                                                                                                                                                                                                  | CMOS push-pull  | Input          |

| 13 - 16  | P0C <sub>0</sub> - P0C <sub>3</sub>  | Port 0C  • 4-bit input/output port  • Input/output setting allowed in units of 1 bit                                                                                                                                                                                                                   | CMOS push-pull  | Input          |

| 17       | INT                                  | External interrupt request or sensor signal                                                                                                                                                                                                                                                            | _               | Input          |

| 18       | P0D <sub>0</sub> /SCK                | Pin for port 0D, timer output, serial data input, serial data output, and serial clock input/output  POD0 - POD3  4-bit input/output port  Input/output setting allowed in units of 1 bit  Pull-up resistor incorporation specifiable by mask option in units of 1 bit  SCK  Serial clock input/output | N-ch open drain | Input<br>(P0D) |

| 19       | P0D <sub>1</sub> /SO                 | SO     Serial data output                                                                                                                                                                                                                                                                              |                 |                |

| 20       | P0D <sub>2</sub> /SI                 | SI     Serial data input                                                                                                                                                                                                                                                                               |                 |                |

| 21       | P0D <sub>3</sub> /TMOUT              | TMOUT     Timer output                                                                                                                                                                                                                                                                                 |                 |                |

| 22<br>23 | P0E <sub>0</sub><br>P0E <sub>1</sub> | Port 0E                                                                                                                                                                                                                                                                                                | N-ch open drain | Input          |

| 24       | V <sub>DD</sub>                      | Power supply                                                                                                                                                                                                                                                                                           | _               | -              |

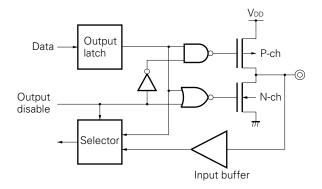

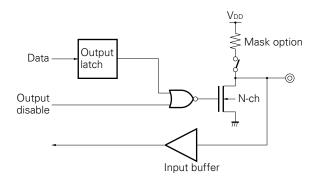

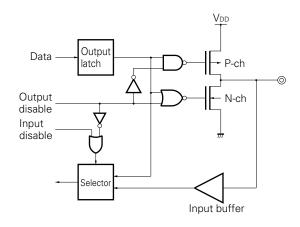

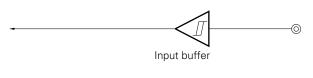

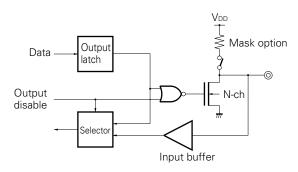

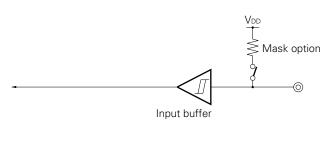

#### 3.2 PIN EQUIVALENT CIRCUIT

Below are simplified diagrams of the input/output circuits for each pin.

#### (1) P0A<sub>0</sub> - P0A<sub>3</sub>, P0B<sub>0</sub> - P0B<sub>3</sub>

#### (4) P0E<sub>0</sub>, P0E<sub>1</sub>

#### (2) POC<sub>0</sub> - POC<sub>3</sub>

#### (5) INT

Schmit trigger input with hysteresis characteristics

#### (3) POD<sub>0</sub> - POD<sub>3</sub>

# (6) RESET

Schmit trigger input with hysteresis characteristics

#### **★ 3.3 HANDLING UNUSED PINS**

Connect unused pins as follows:

**Table 3-1 Handling Unused Pins**

| Pin  |                                                                                 | Dim                                | Recommended cond                                                                        | ditions and handling             |

|------|---------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------|

| FIII |                                                                                 |                                    | Internal                                                                                | External                         |

| Port | Input                                                                           | POA, POB, POC                      | _                                                                                       | Connect to VDD or ground through |

|      | mode                                                                            | POD, POE                           | Pull-up resistors that can be specified with the mask option are not incorporated.      | resistors for each pin.Note 1    |

|      |                                                                                 |                                    | Pull-up resistors that can be specified with the mask option are incorporated.          | Leave open.                      |

|      | Output<br>mode                                                                  | P0A, P0B, P0C<br>(CMOS ports)      | _                                                                                       | Leave open.                      |

|      |                                                                                 | P0D, P0E (N-ch<br>open-drain port) | Outputs low level without pull-up resistors that can be specified with the mask option. |                                  |

|      |                                                                                 |                                    | Outputs low level with pull-up resistors that can be specified with the mask option.    |                                  |

| Exte | rnal inte                                                                       | rrupt (INT)Note 2                  | _                                                                                       | Connect directly to ground.      |

| (whe | RESETNote 3 (when only the built-in power-on/power-down reset function is used) |                                    | Pull-up resistors that can be specified with the mask option are not incorporated.      | Connect directly to VDD.         |

| used |                                                                                 |                                    | Pull-up resistors that can be specified with the mask option are incorporated.          |                                  |

- Notes 1. When a pin is pulled up to VDD (connected to VDD through a resistor) or pulled down to ground (connected to ground through a resistor) outside the chip, take the driving capacity and maximum current consumption of a port into consideration. When using high-resistance pull-up or pull-down resistors, apply appropriate countermeasures to ensure that noise is not attracted by the resistors. Although the optimum pull-up or pull-down resistor varies with the application circuit, in general, a resistor of 10 to 100 kilohms is suitable.

- 2. Since the INT pin is also used for setting the test mode, connect it directly to ground when the pin is not used.

- 3. When designing an application circuit which requires high reliability, be sure to design a circuit to which an external RESET signal can be input. Since the RESET pin is also used for setting the test mode, connect it to VDD directly when not used.

Caution To fix the I/O mode and output level of a pin, it is recommended that they should be specified repeatedly within a loop in a program.

#### 3.4 NOTES ON USE OF THE RESET AND INT PINS

The  $\overline{\text{RESET}}$  and INT pins have the test mode selecting function for testing the internal operation of the  $\mu\text{PD17120}$  (IC test), besides the functions shown in **Section 3.1**.

Applying a voltage exceeding  $V_{DD}$  to the  $\overline{RESET}$  or INT pin causes the  $\mu PD17120$  to enter the test mode. When noise exceeding  $V_{DD}$  comes in during normal operation, the device is switched to the test mode.

For example, if the wiring from the RESET or INT pin is too long, noise may be induced on the wiring, causing this mode switching.

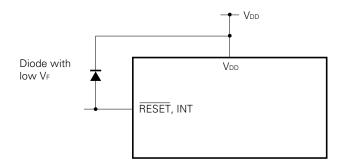

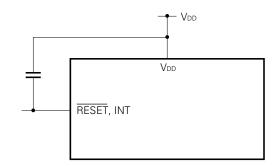

When installing the wiring, lay the wiring in such a way that noise is suppressed as much as possible. If noise yet arises, use an external part to suppress it as shown below.

Connect a diode with low V<sub>F</sub> between the pin and V<sub>DD</sub>.

Connect a capacitor between the pin and V<sub>DD</sub>.

#### 4. PROGRAM MEMORY (ROM)

The  $\mu$ PD17120 is loaded with a 1.5K-byte (768  $\times$  16 bit) mask ROM as program memory.

The program memory address is specified by the program counter.

★ Program memory stores the program and the constant data table. The reset start address and interrupt vector addresses are assigned to 0000H to 0003H in program memory.

#### 4.1 PROGRAM MEMORY ORGANIZATION

Fig. 4-1 shows a program memory map. Branch instructions, subroutine calls, and table references can specify any address in program memory.

Address 0000H Reset start address O Subroutine entry address specified in Serial interface 0001H CALL addr instruction interrupt vector 0002H Timer interrupt vector O Branch address specified in BR addr instruction External input (INT) 0003H interrupt vector Branch address specified in BR @AR instruction O Subroutine entry address specified in CALL @AR instruction Table reference address specified in MOVT DBF, @AR instruction 02FFH 16 bits

Fig. 4-1 Program Memory Map for  $\mu$ PD17120

#### 5. PROGRAM COUNTER (PC)

The program counter is used to specify an address in program memory.

#### 5.1 PROGRAM COUNTER CONFIGURATION

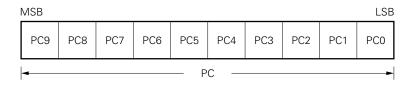

As shown in Fig. 5-1, the program counter is a 10-bit binary counter.

Fig. 5-1 Program Counter

#### 5.2 PROGRAM COUNTER OPERATION

Normally, the program counter is automatically incremented each time a command is executed. The memory address at which the next instruction to be executed is stored is assigned to the program counter under the following conditions: At reset; when a branch, subroutine call, return, or table referencing instruction is executed; or when an interrupt is received.

Table 5-1 Value of the Program Counter after an Instruction Is Executed

| Program counter                     | Program counter value                                                                |                                  |      |     |     |     |     |     |     |     |

|-------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|------|-----|-----|-----|-----|-----|-----|-----|

| Instruction                         | PC9                                                                                  | PC8                              | PC7  | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

| During reset                        | 0                                                                                    | 0                                | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| BR addr                             | Value                                                                                | oot by                           | oddr |     |     |     |     |     |     |     |

| CALL addr                           | Value set by addr                                                                    |                                  |      |     |     |     |     |     |     |     |

| BR @AR<br>CALL @AR<br>MOVT DBF, @AR | Value in the address register (AR)                                                   |                                  |      |     |     |     |     |     |     |     |

| RET<br>RETSK<br>RETI                | Value in the address stack location pointed to by the stack pointer (return address) |                                  |      |     |     |     |     |     |     |     |

| During interrupt                    | Vecto                                                                                | Vector address for the interrupt |      |     |     |     |     |     |     |     |

#### 5.3 NOTES ON USING THE PROGRAM COUNTER

The program counter (PC) of the  $\mu$ PD17120 is a 10-bit counter which can specify a program as large as 1024 steps. However, the ROM can contain only 768 steps (at addresses 0000H to 02FFH). If the program counter specifies address 300H or higher, the counter reads the contents of address FFFFH, and enters into a status equivalent to when instruction "SKF PSW, #0FH" is executed.

Therefore, the following guidelines should be observed.

- (1) When a program consists of up to 768 steps (up to address 02FFH), use a branch instruction (BR) or a return instruction (RET) at the end of the program. If neither a branch nor a return instruction is used, the program counter will not automatically be set to address 0000H, but will instead specify an address for which no ROM exists.

- (2) Do not use instructions which branch to addresses after the 768th step (address 02FFH).

#### 6. STACK

Fig. 6-1 shows the stack configuration. The stack consists of five address stack registers and one interrupt stack register.

The stack is used to save the return address during execution of subroutine calls and table reference instructions. When an interrupt occurs, the program return address and the program status work (PSWORD) are automatically saved in the stack. Then, all bits of the bank and PSWORD are cleared to 0.

Stack pointer Address stack register (SP) (ASR) bо b<sub>2</sub> b<sub>1</sub> b٥ bв b<sub>7</sub> b<sub>6</sub> bъ b4 рз b<sub>2</sub> b<sub>1</sub> SPb<sub>2</sub> SPb<sub>1</sub> SPbo **►** 0H Address stack register 0 ► 1H Address stack register 1 **►** 2H Address stack register 2 **►** 3H Address stack register 3 Address stack register 4 **►** 4H Interrupt stack register (INTSK) BCDSK0 CMPSK0 CYSK0 ZSK0 IXESK0

Fig. 6-1 Stack Configuration

#### 7. DATA MEMORY (RAM)

Data memory (RAM) stores data such as operation and control data. Data can be read from or written to data memory with an instruction during normal operation.

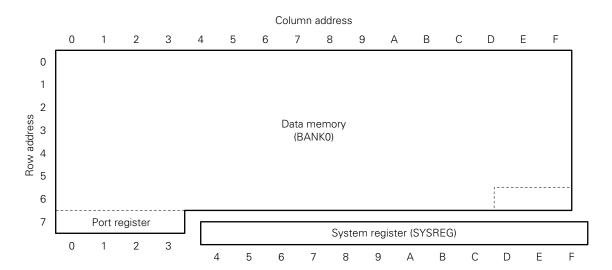

#### 7.1 DATA MEMORY ORGANIZATION

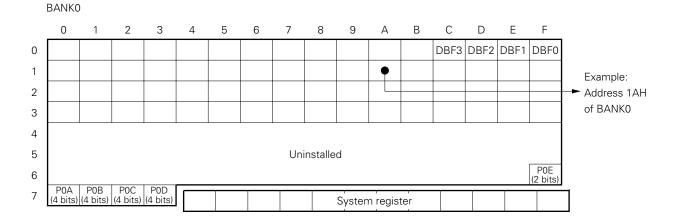

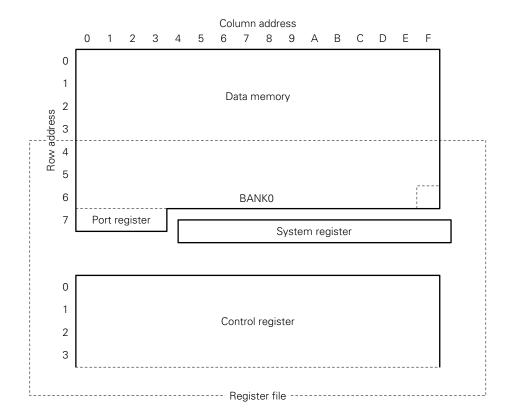

Data memory locations have 7-bit addresses. The three high-order bits of each address are called the row address, and the four low-order bits are called the column address.

For example, the row address of address 1AH is 1H. The column address is 0AH.

Each addressed memory location is 4-bits (one nibble) long.

Data memory contains an area to which the user is allowed to store data freely, as well as areas which are reserved for the use of specific functions.

The areas reserved for specific functions are as follows:

System register (SYSREG) (See Chapter 9.)

Data buffer (DBF) (See Chapter 11.)

Port registers (See Chapter 13.)

Fig. 7-1 Organization of Data Memory

#### 7.2 UNINSTALLED DATA MEMORY

There is no hardware installed for addresses 40H to 6EH. Any attempt to read from this area will yield an unpredictable value. Any instructions to write data to this area are invalid and must not be used.

If this uninstalled data memory area is used by a 17K-series assembly (AS17K) program or by an in-circuit emulator (IE-17K or IE-17K-ET), the following occurs:

AS17K: An error is indicated.

IE-17K or IE-17K-ET: Write instructions are invalidated and read instructions read 0.

#### 8. GENERAL REGISTER (GR)

The general register, as the name implies, is a general register used for data transfer and manipulation. In the 17K series, the location of the general register is not fixed. The area used for the general register is in data memory, as specified by the general register pointer (RP). Thus, part of the data memory area can be specified as the general register as required, allowing data transfer in data memory and data memory manipulation to be performed with a single instruction.

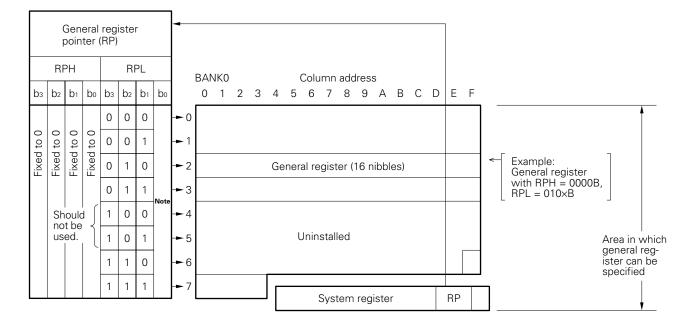

#### 8.1 GENERAL REGISTER POINTER (RP)

RP is a pointer used to specify part of data memory as the general register. In RP, specify a desired data memory bank and row address for the general register. RP consists of seven bits: 7DH (RPH), and the three high-order bits of 7EH (RPL) in the system register (see **Chapter 9**).

Set a bank in RPH, and a data memory row address in RPL.

Fig. 8-1 General Register Pointer Configuration

Note Allocated to the flag BCD

#### 9. SYSTEM REGISTER (SYSREG)

The system register (SYSREG), located in data memory, is used for direct control of the CPU.

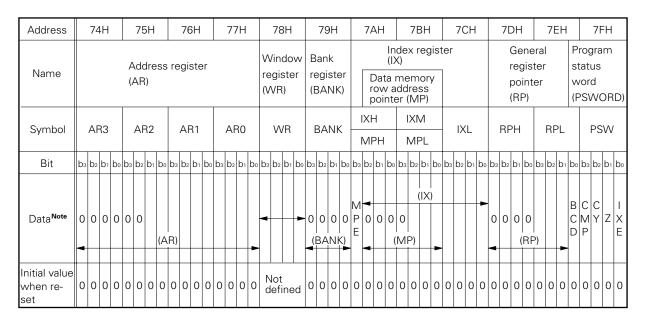

#### 9.1 SYSTEM REGISTER CONFIGURATION

Fig. 9-1 shows the allocation address of the system register in data memory. As shown in Fig. 9-1, the system register is allocated in addresses 74H to 7FH of data memory.

Since the system register is allocated in data memory, it can be manipulated using any of the instructions available for manipulating data memory. Therefore, it is also possible to put the system register in the general register.

Fig. 9-1 Allocation of System Register in Data Memory

Fig. 9-2 shows the configuration of the system register. As shown in Fig. 9-2, the system register consists of the following seven registers.

Address register

Window register

Bank register

Index register

Data memory row address pointer

General register pointer

Program status word

(AR)

(BANK)

(IX)

(BANK)

(IX)

(PSWORD)

Fig. 9-2 System Register Configuration

Note A bit for which 0 is written is fixed at 0.

★ Remark Once the contents of PSWORD are saved in the interrupt stack register, all the five bits of PSWORD are cleared to 0.

#### 10. REGISTER FILE (RF)

The register file is a register used mainly for specifying conditions for peripheral hardware.

The register file can be controlled using dedicated instructions PEEK and POKE or AS17K macro instructions SETn, CLRn, and INITFLG.

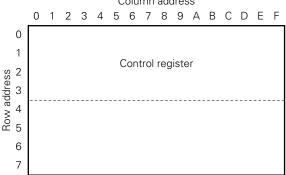

#### 10.1 REGISTER FILE CONFIGURATION

#### 10.1.1 Configuration of the Register File

Fig. 10-1 shows the configuration of the register file.

As shown in Fig. 10-1, the register file is a register consisting of 128 nibbles (128  $\times$  4 bits).

In the same way as with data memory, the register file is divided into addresses in units of four bits. It has a total of 128 nibbles specified in row addresses from 0H to 7H and column addresses from 0H to 0FH. Address locations 00H to 3FH define an area called the control register.

Column address

Fig. 10-1 Register File Configuration

#### 10.1.2 Relationship between the Register File and Data Memory

Fig. 10-2 shows the relationship between the register file and data memory.

As shown in Fig. 10-2, the register file overlaps with data memory at addresses 40H to 7FH.

This means that, on a program, it seems that the same memory exists in the register file at addresses 40H to 7FH and in the data memory at addresses 40H to 7FH.

Fig. 10-2 Relationship Between the Register File and Data Memory

#### 10.2 FUNCTIONS OF THE REGISTER FILE

#### 10.2.1 Functions of the Register File

The register file is a collection of registers in which peripheral hardware conditions are set with the PEEK instruction or POKE instruction.

The register used to control the peripheral hardware is located at addresses 00H to 3FH. This area is called the control register.

Addresses 40H to 7FH of the register file constitute normal data memory. Thus, not only the MOV instruction, but also the PEEK and POKE instructions, can be used to enable this part to perform read and write operations.

#### 10.2.2 Control Register Functions

The peripheral hardware whose conditions can be controlled by control registers is listed below.

For details concerning peripheral hardware and the control register, see the section for the peripheral hardware concerned.

- Ports

- 8-bit timer counter (TM)

- Serial interface (SIO)

- · Interrupt function

- Stack pointer (SP)

#### 11. DATA BUFFER (DBF)

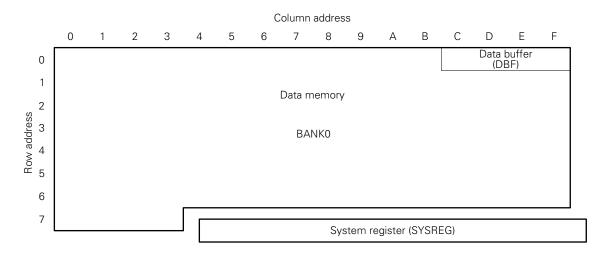

The data buffer consists of four nibbles allocated in addresses 0CH to 0FH in BANK0.

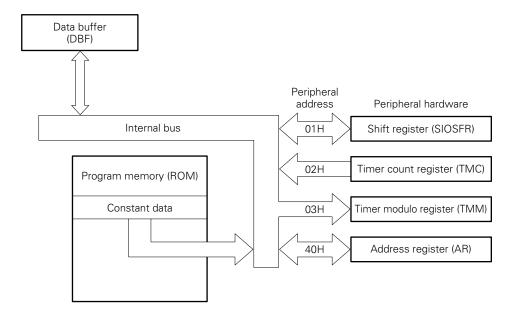

The data buffer acts as a data storage area for the CPU peripheral hardware (address register, serial interface, and timer) through use of the GET and PUT instructions. It also acts as data storage used for receiving and transferring data. By using the MOVT DBF, and @AR instructions, fixed data in program memory can be read into the data buffer.

#### 11.1 DATA BUFFER CONFIGURATION

Fig. 11-1 shows the allocation of the data buffer in data memory.

As shown in Fig. 11-1, the data buffer is allocated in address locations 0CH to 0FH in data memory and consists of 4 nibbles  $(4 \times 4 \text{ bits})$ , totaling 16 bits.

Fig. 11-1 Allocation of the Data Buffer

Fig. 11-2 shows the configuration of the data buffer. As shown in Fig. 11-2, the data buffer is made up of sixteen bits with its least significant bit in bit 0 of address 0FH and its most significant bit in bit 3 of address 0CH.

Address 0CH 0DH 0EH 0FH Data memory BANK0 Bit bз b<sub>1</sub> bo рз bo b<sub>2</sub> b<sub>2</sub> b<sub>1</sub> bо bз b<sub>2</sub> b<sub>1</sub> bo bз b<sub>2</sub> b<sub>1</sub> Bit b14 b13 b<sub>12</sub> b10 b9 b<sub>5</sub> b4 b<sub>1</sub> b<sub>6</sub> Data buffer DBF3 DBF0 Symbol DBF2 DBF1 ^ M S B Data Data

Fig. 11-2 Data Buffer Configuration

Because the data buffer is allocated in data memory, it can be used in any of the data memory manipulation instructions.

#### 11.2 FUNCTIONS OF THE DATA BUFFER

The data buffer has two separate functions.

The data buffer is used for data transfer with peripheral hardware. The data buffer is also used for reading constant data in program memory. Fig. 11-3 shows the relationship between the data buffer and peripheral hardware.

Fig. 11-3 Relationship Between the Data Buffer and Peripheral Hardware

#### 12. ALU BLOCK

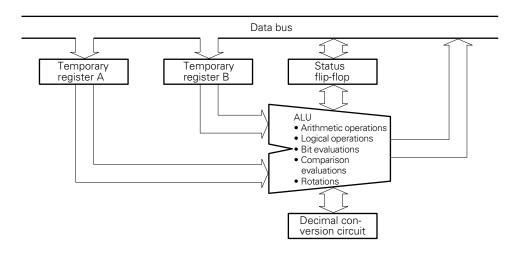

The ALU is used for performing arithmetic operations, logical operations, bit evaluations, comparison evaluations, and rotations on 4-bit data.

#### 12.1 ALU BLOCK CONFIGURATION

Fig. 12-1 shows the configuration of the ALU block.

As shown in Fig. 12-1, the ALU block consists of the main 4-bit data processor, temporary registers A and B, the status flip-flop for controlling the status of the ALU, and the decimal conversion circuit for use during arithmetic operations in BCD.

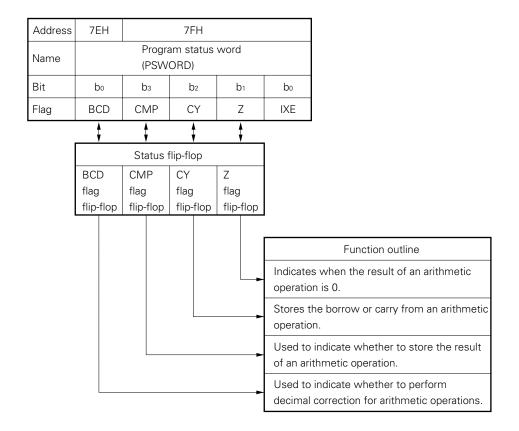

As shown in Fig. 12-1, the status flip-flop consists of the following flags: Zero flag flip-flop, carry flag flip-flop, compare flag flip-flop, and the BCD flag flip-flop.

Each flag in the status flip-flop corresponds directly to a flag in the program status word (PSWORD: addresses 7EH, 7FH) located in the system register. The flags in the program status word are the following: Zero flag (Z), carry flag (CY), compare flag (CMP), and the BCD flag (BCD).

Fig. 12-1 Configuration of the ALU

#### 13. PORTS

#### 13.1 PORT 0A (P0A<sub>0</sub>, P0A<sub>1</sub>, P0A<sub>2</sub>, P0A<sub>3</sub>)

Port 0A is a 4-bit input/output port with an output latch. It is mapped into address 70H in data memory. The output format is CMOS push-pull output.

Input or output can be specified bit-by-bit. Input/output can be specified by P0ABIO0 to P0ABIO3 (address 35H) in the register file.

At reset, P0ABIOn is 0 (n = 0 to 3) and all P0A pins are input ports. The contents of the port output latch are 0.

Table 13-1 Writing into and Reading from the Port Register (0.70H)

(n = 0 to 3)

| P0ABIOn | Pin input/output    | BANK                   | 0 70H              |

|---------|---------------------|------------------------|--------------------|

| RF: 35H | i iii iiiput/output | Write                  | Read               |

| 0       | Input               | Possible               | P0A pin status     |

| 1       | Output              | Write to the P0A latch | P0A latch contents |

#### 13.2 PORT 0B (P0B<sub>0</sub>, P0B<sub>1</sub>, P0B<sub>2</sub>, P0B<sub>3</sub>)

Port 0B is a 4-bit input/output port with an output latch. It is mapped into address 71H of BANK0 in data memory. The output format is CMOS push-pull output.

Input or output can be specified in 4-bit units. Input/ output is specified by P0BGIO (bit 0 in address 24H) in the register file.

At reset, P0BGIO is 0 and all P0B pins are input ports. The value of the port 0B output latch is 0.

Table 13-2 Writing into and Reading from the Port Register (0.71H)

| POBGIO         | Pin input/output    | BANK0 71H              |                    |  |

|----------------|---------------------|------------------------|--------------------|--|

| RF: 24H, bit 0 | i iii iiiput/output | Write                  | Read               |  |

| 0              | Input               | Possible               | P0B pin status     |  |

| 1              | Output              | Write to the P0B latch | P0B latch contents |  |

#### 13.3 PORT 0C (P0C<sub>0</sub>, P0C<sub>1</sub>, P0C<sub>2</sub>, P0C<sub>3</sub>)

Port 0C is a 4-bit input/output port with an output latch. It is mapped into address 72H of BANK0 in data memory. The output format is CMOS push-pull output.

Input or output can be specified bit-by-bit. Input/output can be specified by P0CBIO0 to P0CBIO3 (address 34H) in the register file.

At reset, P0CBIOn is 0 (n = 0 to 3) and all P0C pins are input ports. The contents of the port output latch are 0.

Table 13-3 Writing into and Reading from the Port Register (0.72H)

(n = 0 to 3)

| P0CBIOn | Pin input/output    | BANK0 72H              |                    |  |

|---------|---------------------|------------------------|--------------------|--|

| RF: 34H | i iii iiipui/output | Write                  | Read               |  |

| 0       | Input               | Possible               | POC pin status     |  |

| 1       | Output              | Write to the P0C latch | P0C latch contents |  |

#### 13.4 PORT 0D (P0D<sub>0</sub>/SCK, P0D<sub>1</sub>/SO, P0D<sub>2</sub>/SI, P0D<sub>3</sub>/TMOUT)

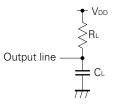

Port 0D is a 4-bit input/output port with an output latch. It is mapped into address 73H in data memory. The output format is N-ch open-drain output. By mask option, the port can contain pull-up resistors bit-by-bit.

Input or output can be specified bit-by-bit. Input/output is specified with P0DBIO0 to P0DBIO3 (address 33H) in the register file.

At reset, P0DBIOn is set to 0 (n = 0 to 3) and all P0D pins become input ports. The contents of the port output latch become 0. The output latch contents remain unchanged even if P0DBIOn changes from 1 to 0.

Port 0D can also be used for serial interface input/output or timer output. SIOEN (bit 0 in address 0AH) in the register file is used to switch ports ( $P0D_0$  to  $P0D_2$ ) to serial interface input/output ( $\overline{SCK}$ , SI, SO) and vice versa. TMOSEL (bit 0 in address 12H) in the register file is used to switch a port ( $P0D_3$ ) to timer output ( $\overline{TMOUT}$ ) and vice versa. If TMOSEL = 1 is selected, 1 is output at timer reset. This output is inverted every time a timer count value matches the modulo register contents.

Table 13-4 Register File Contents and Pin Functions

(n = 0 to 3)

| Register file value |                  |                    |                       | Pin fu                  | nction |             |

|---------------------|------------------|--------------------|-----------------------|-------------------------|--------|-------------|

| TMOSEL<br>RF: 12H   | SIOEN<br>RF: 0AH | P0DBIOn<br>RF: 33H | P0D <sub>0</sub> /SCK | P0D <sub>3</sub> /TMOUT |        |             |

| Bit 0               | Bit 0            |                    |                       |                         |        |             |

|                     | 0                | 0                  |                       |                         |        |             |

| 0                   | 0                | 1                  |                       |                         |        |             |

|                     | 1                | 0                  | SCK                   | so                      | SI     | Input port  |

|                     | '                | 1                  | SCK                   | 50                      | 51     | Output port |

|                     | 0                | 0                  | Input port            |                         |        |             |

| 1                   | 0                | 1                  |                       | Output port             |        | TMOUT       |

| , I                 | 1                | 0                  | SCK                   | so                      | CI     | TIVIOUT     |

|                     | Į į              | 1                  | SCK                   | 30                      | SI     |             |

Table 13-5 Contents Read from the Port Register (0.73H)

|            | Port mode                                        | Contents read from the port register (0.73H) |  |  |

|------------|--------------------------------------------------|----------------------------------------------|--|--|

| Input port |                                                  | Pin status                                   |  |  |

| Outpu      | t port                                           | Output latch contents                        |  |  |

|            | An internal clock is selected as a serial clock. | Output latch contents                        |  |  |

| SCK        | An external clock is selected as a serial clock. | Pin status                                   |  |  |

| so         |                                                  | UndefinedNote                                |  |  |

| SI         |                                                  | Pin status                                   |  |  |

| TMOU       | Т                                                | Output latch contents                        |  |  |

Note See Chapter 15 for details.

#### 13.5 PORT 0E (P0E<sub>0</sub>, P0E<sub>1</sub>)

Port 0E is a 2-bit input/output port with an output latch. It is mapped into bits 0 and 1 in address 6FH in data memory. The output format is N-ch open-drain output. By mask option, the port can contain pull-up resistors bit-by-bit.

Input or output can be specified bit-by-bit. Input/output is specified by P0EBIO0 and P0EBIO1 (bits 0 and 1 in address 32H) in the register file.

When a read instruction is executed, not the output latch data but the pin status is read regardless of the input or output mode.

At reset, P0EBIOn is set to 0 (n = 0 and 1) and each P0E pin becomes input port. The contents of the port output latch are 0.

The write instruction specified for bits 2 and 3 of address 6FH is invalidated. If it is executed, 0 is read out.

Table 13-6 Writing into and Reading from the Port Register (0.6FH.0 and 0.6FH.1)

(n = 0 and 1)

| P0EBIOn | Pin input/output    | BANK0 6FH                     |        |  |

|---------|---------------------|-------------------------------|--------|--|

| RF: 32H | i iii iiiput/output | Write                         | Read   |  |

| 0       | Input               | Possible                      | DOEitt |  |

| 1       | Output              | Write to the P0E output latch |        |  |

#### **★ 13.6 NOTES ON MANIPULATING PORT REGISTERS**

The states of only the port 0E pins of the  $\mu$ PD17120 can be read even when the port pins have been set to output mode.

When a port register is manipulated with a built-in macro instruction (such as SETn or CLRn) or an AND, OR, or XOR instruction, the states of those pins for which the state should remain unchanged may change unexpectedly.

Especially when the port 0E pins are set to low externally, always take the possibility of this change in the states of the pins into consideration.

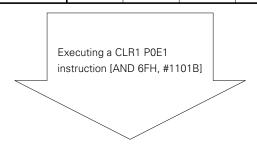

When a CLR1 P0E1 instruction (identical to an AND 6FH, #1101B instruction) is applied to the port 0E pins, the corresponding port register and internal states are changed, as shown in Fig. 13-1.

Assume that the states of port 0E are those shown in Fig. 13-1 #. Pins P0E<sub>1</sub> and P0E<sub>0</sub>, both used as output pins, output high level, while pin P0E<sub>0</sub> forcibly set to low externally.

Although the  $\mu$ PD17120 does not support pins P0E<sub>3</sub> and P0E<sub>2</sub>, they are virtually assumed to exist within a program.

When a CLR1 P0E1 instruction is executed to set pin P0E<sub>1</sub> to low, the states of the port 0E pins change as shown in Fig. 13-1 \$. The port register changes such that pin P0E<sub>1</sub> output low level and pin P0E<sub>0</sub>, required to output high level, actually output low level. This is because the CLR1 P0E1 instruction has been applied to the states of the port 0E pins, but not to the states of the port register.

To prevent this problem, use another instruction, such as a MOV instruction, to specify the states of all port 0E pins, not merely the states of those pins whose states are to be changed. In this example, it is recommended that a MOV 6FH, #1101B instruction be used to set only pin P0E<sub>1</sub> to low.

Fig. 13-1 Changes in the Port Register According to the Execution of a CLR1 P0E1 Instruction

# POE3 POE2 POE1 POE0 Port register Does not exist. 1 1 Internal state — — H output H output

L (forcible)

### # Before the instruction is executed

Pin state

#### \$ After the instruction is executed

|                | Р0Ез   | P0E <sub>2</sub> | P0E <sub>1</sub> | P0E₀     |

|----------------|--------|------------------|------------------|----------|

| Port register  | Does n | ot exist.        | 0                | 0        |

| Internal state | _      | _                | L output         | L output |

| Pin state      | 1      | _                | L                | L        |

H: High level, L: Low level

#### 14. 8-BIT TIMER COUNTER (TM)

An 8-bit timer counter is incorporated in  $\mu$ PD17120.

The timer is controlled by hardware operation with the PUT/GET instruction or by register operation in the register file with the PEEK/POKE instruction.

#### 14.1 CONFIGURATION OF 8-BIT TIMER COUNTER

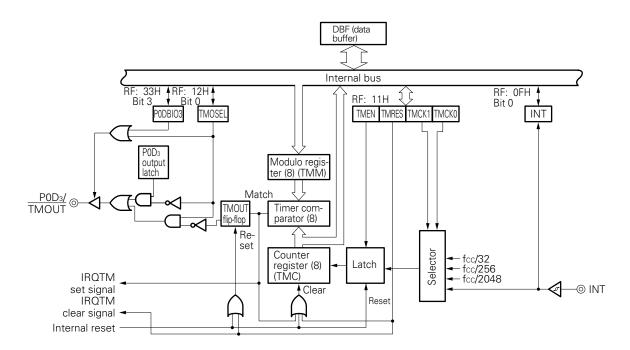

Fig. 14-1 shows the configuration of the 8-bit timer counters. An 8-bit timer counter consists of an 8-bit counter register, 8-bit modulo register, comparator (compares counter register values and modulo register values), and selector (for count pulse selection).

Caution The modulo register is a write-only register.

The counter register is a read-only register.

Fig. 14-1 Configuration of the 8-Bit Timer Counter

**Table 14-1 Source Clock**

| Register | file value | Source clock to be selected         |  |  |

|----------|------------|-------------------------------------|--|--|

| TMCK1    | TMCK0      |                                     |  |  |

| 0        | 0          | fcc/256                             |  |  |

| 0        | 1          | fcc/32                              |  |  |

| 1        | 0          | fcc/2048                            |  |  |

| 1        | 1          | External clock input to the INT pir |  |  |

\*

#### 14.2 OUTPUTTING A TIMER SIGNAL

The P0D<sub>3</sub>/TMOUT pin functions as a timer match signal output pin when the TMOSEL flag is set to 1. The P0DBIO3 value has nothing to do with this setting.

The timer contains a match signal output flip-flop. It reverses the output each time the comparator of the 8-bit timer outputs a match signal. When the TMOSEL flag is set to 1, the contents of this flip-flop are output to the  $P0D_3/\overline{TMOUT}$  pin.

The P0D<sub>3</sub>/TMOUT pin is an N-ch open-drain output pin. The mask option enables this pin to contain a pull-up resistor. If this pin does not contain a pull-up resistor, its initial status is high impedance.

An internal timer output flip-flop starts operating when TMEN is set to 1. To make the flip-flop start output beginning at an initial value, set 1 in TMRES and reset the flip-flop.

#### 15. SERIAL INTERFACE (SIO)

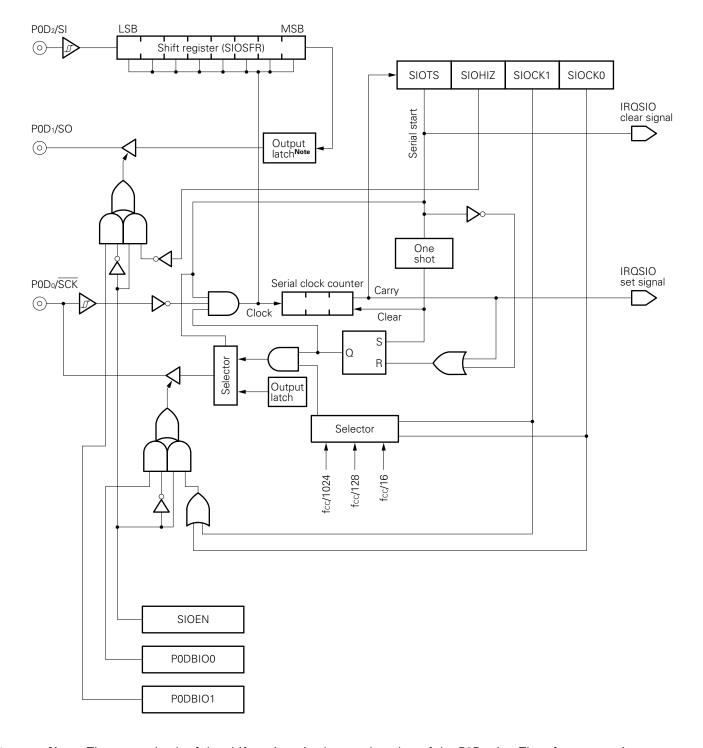

The serial interface consists of an 8-bit shift register (SIOSFR), serial mode register, and serial clock counter. It is used for serial data input/output.

#### 15.1 FUNCTIONS OF THE SERIAL INTERFACE

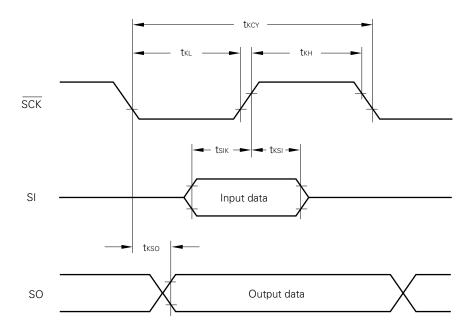

This serial interface provides three signal lines: serial clock input pin (SCK), serial data output pin (SO), and serial data input pin (SI). It allows 8 bits to be sent or received in synchronization with clocks. It can be connected to peripheral input/output devices using any method with a mode compatible to that used by the  $\mu$ PD7500 or 75X series.

#### (1) Serial clock

Three types of internal clocks and one type of external clock are able to be selected. If an internal clock is selected as a serial clock, it is automatically output to the POD<sub>0</sub>/SCK pin.

| Register | file value | Chiff alsolute has a lasted                          |  |

|----------|------------|------------------------------------------------------|--|

| SIOCK1   | SIOCK0     | Shift clock to be selected                           |  |

| 0        | 0          | External clock input to the $\overline{\sf SCK}$ pin |  |

| 0        | 1          | fcc/16                                               |  |

| 1        | 0          | fcc/128                                              |  |

| 1        | 1          | fcc/1024                                             |  |

Table 15-1 Shift Clock

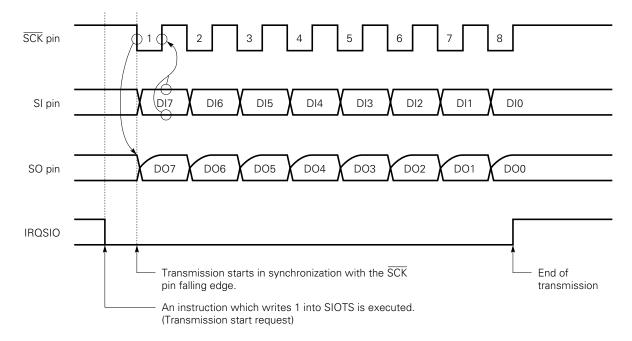

#### (2) Transmission

When SIOEN is set to 1, the pins of port 0D (P0Do/SCK, P0D1/SO, P0D2/SI) function as the pins of the serial interface. The serial interface operates in synchronization with the falling edge of the external or internal clock by setting SIOTS to 1. When SIOTS is set to 1, IRQSIO is automatically cleared.

Transmission starts from the most significant bit of the shift register in synchronization with the falling edge of the serial clock. SI pin information is stored in the shift register starting at the most significant bit in synchronization with the rising edge of the serial clock.

When the transfer of 8-bit data is completed, SIOTS is automatically cleared to 0 and IRQSIO is set to 1.

**Remark** Serial transmission starts only from the most significant bit of the shift register contents. It is not possible to start transmission from the least significant bit. SI pin status is always stored in the shift register in synchronization with the rising edge of the serial clock.

Fig. 15-1 Block Diagram of the Serial Interface

**Note** The output latch of the shift register is also used as that of the P0D₁ pin. Therefore, executing an output instruction for the P0D₁ pin changes the output latch status of the shift register.

#### 15.2 3-WIRE SERIAL INTERFACE OPERATION MODES

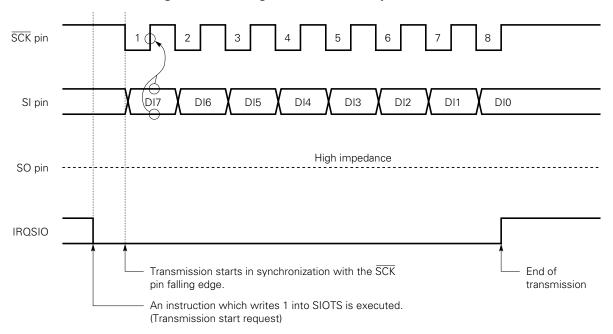

Two modes can be used for the serial interface. If the serial interface function is selected, the P0D<sub>2</sub>/SI pin always takes in data in synchronization with the serial clock.

- · 8-bit transmission and reception mode (simultaneous transmission and reception)

- 8-bit reception mode (with the SO pin set to the high impedance status)

Table 15-2 Serial Interface Operation Mode

| SIOEN | SIOHIZ | P0D2/SI pin | P0D1/SO pin  | Serial interface operation mode       |  |

|-------|--------|-------------|--------------|---------------------------------------|--|

| 1     | 0      | SI          | so           | 8-bit transmission and reception mode |  |

| 1     | 1      | SI          | P0D1 (input) | 8-bit reception mode                  |  |

| 0     | ×      | P0D2 (I/O)  | P0D1 (I/O)   | General port mode                     |  |

x: Don't care

#### (1) 8-bit transmission and reception mode (simultaneous transmission and reception)

Serial data input/output is controlled by a serial clock. The most significant bit of the shift register is output from the SO line with a falling edge of the serial clock ( $\overline{SCK}$ ). The contents of the shift register is shifted one bit and at the same time, data on the SI line is loaded into the least significant bit of the shift register. The serial clock counter counts serial clock pulses. Every time it counts eight clocks, the internal interrupt request flag is set to 1 (IRQSIO  $\leftarrow$  1).

Fig. 15-2 Timing of 8-Bit Transmission and Reception Mode (Simultaneous Transmission and Reception)

Remark Dln: Input serial data

DOn: Output serial data

#### (2) 8-bit transmission and reception mode (SO pin in the high impedance status)

When SIOHIZ is 1, the P0D<sub>1</sub>/SO pin is in the high impedance status. If serial clock supply starts by writing 1 in SIOTS, only the reception function of the serial interface operates.

The P0D<sub>1</sub>/SO pin is in the high impedance status and can be used for input port (P0D<sub>1</sub>).

Fig. 15-3 Timing of the 8-Bit Reception Mode

Remark Dln: Input serial data

#### (3) Operation stop mode

If the value in SIOTS (RF: 1AH, bit 3) is 0, the serial interface enters operation stop mode. In this mode, no serial transfer occurs.

In this mode, the shift register does not perform shifting and can be used as an ordinary 8-bit register.

#### 16. INTERRUPT FUNCTIONS

The  $\mu$ PD17120 has two internal interrupt functions and one external interrupt function. It can be used in various applications.

The interrupt control circuit of the  $\mu$ PD17120 has the features listed below. This circuit enables very high-speed interrupt handling.

- (a) Used to determine whether an interrupt can be accepted with the interrupt mask enable flag (INTE), which is controlled by the EI or DI instruction, and interrupt enable flag (IPxxx).

- (b) The interrupt request flag (IRQxxx) can be tested or cleared. (Interrupt generation can be checked by software.)

- (c) Standby mode (STOP, HALT) can be released by an interrupt request. (Release source can be selected by the interrupt enable flag.)

- Cautions 1. In interrupt handling, the BCD, CMP, CY, Z, and IXE flags are saved in the stack automatically by the hardware for up to three levels of multiple interrupts. The DBF and WR are not saved by the hardware when peripheral hardware such as the timer or serial interface is accessed in interrupt handling. It is recommended that the DBF and WR be saved in RAM by the software at the beginning of interrupt handling. Saved data can be loaded back into the DBF and WR immediately before the end of interrupt handling.

- 2. Since the interrupt stack has only one level, multiple interrupts cannot be performed by hardware. When more than one interrupt is received, the data from the first interrupt is lost.

#### 16.1 INTERRUPT SOURCE TYPES AND VECTOR ADDRESSES

For every interrupt in the  $\mu$ PD17120, when the interrupt is accepted, a branch occurs to the vector address associated with the interrupt source. This method is called the vectored interrupt method. Table 16-1 lists the interrupt source types and vector addresses.

If two or more interrupt requests occur or multiple suspended interrupt requests are enabled at the same time, they are handled according to priorities shown in Table 16-1.

Table 16-1 Interrupt Source Types

| Interrupt source        | Priority | Vector<br>address | IRQ flag                   | IP flag                   | IEG flag                       | Internal/<br>external | Remarks                                                                        |

|-------------------------|----------|-------------------|----------------------------|---------------------------|--------------------------------|-----------------------|--------------------------------------------------------------------------------|

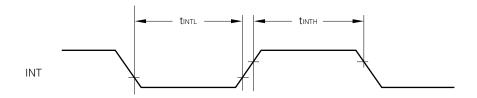

| INT pin (RF:0FH, bit 0) | 1        | 0003H             | IRQ<br>RF:3FH,<br>bit 0    | IP<br>RF:2FH,<br>bit 0    | IEGMD0,1<br>RF:1FH<br>bit 0, 1 | External              | Rising edge, falling edge<br>or rising/falling edge<br>(both) can be selected. |

| Timer                   | 2        | 0002H             | IRQTM<br>RF:3EH,<br>bit 0  | IPTM<br>RF:2FH,<br>bit 1  | -                              | Internal              |                                                                                |

| Serial interface        | 3        | 0001H             | IRQSIO<br>RF:3DH,<br>bit 0 | IPSIO<br>RF:2FH,<br>bit 2 | -                              | Internal              |                                                                                |

\_

#### 16.2 HARDWARE COMPONENTS OF THE INTERRUPT CONTROL CIRCUIT

The flags of the interrupt control circuit are explained below.

#### (1) Interrupt request flag and the interrupt enable flag

The interrupt request flag (IRQ×××) is set to 1 when an interrupt request occurs. When interrupt handling is executed, the flag is automatically cleared to 0.

An interrupt enable flag (IPxxx) is provided for each interrupt request flag. If the flag is 1, an interrupt is enabled. If it is 0, the interrupt is disabled.

#### (2) EI/DI instruction

The EI/DI instruction is used to determine whether an accepted interrupt is to be executed. If the EI instruction is executed, the interrupt enable flag (INTE) for enabling interrupt reception is set. Since the INTE flag is not registered in the register file, flag status cannot be checked by instructions. The DI instruction clears the INTE flag to 0 and disables all interrupts.

At reset the INTE flag is cleared to 0 and all interrupts are disabled.

Table 16-2 Interrupt Request Flag and Interrupt Enable Flag

| Interrupt<br>request flag | Signal for setting the interrupt request flag                                                             | Interrupt<br>enable flag |

|---------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|

| IRQ                       | Set by edge detection of an INT pin input signal.<br>A detection edge is selected by IEGMD0 or<br>IEGMD1. | IP                       |

| IRQTM                     | Set by a match signal from timer.                                                                         | IPTM                     |

| IRQSIO                    | Set by a serial data transmission end signal from the serial interface.                                   | IPSIO                    |

#### 17. STANDBY FUNCTION

#### 17.1 OVERVIEW OF THE STANDBY FUNCTION

The  $\mu$ PD17120 can reduce its current by using the standby function. The standby function supports STOP and HALT modes.

In the STOP mode, the system clock is stopped and the CPU current is reduced to almost only a leak current. This mode is useful in retaining data memory contents without operating the CPU.

In the HALT mode, the oscillation of the system clock continues. However, the system clock is not supplied to the CPU, stopping CPU operation. In this mode, current reduction is less than that in the STOP mode. However, since the system clock is oscillating, operation can be started immediately after the HALT mode is released. In both STOP and HALT modes, the statuses of the data memory, registers, and output latches of the output port used immediately before the standby mode is set are maintained (except STOP 0000B). Therefore, in order to lower consumption current for the entire system, input/output port statuses should be set beforehand.

STOP mode HALT mode Programmed instruction STOP instruction **HALT** instruction Clock oscillator Oscillation stopped Oscillation continued CPU · Operation stopped **RAM** • The contents held immediately before setting standby mode are retained. Port • The status existing immediately before setting standby mode is retained. Note Opera-TM · Operation stopped. Operable tion (The count is reset to 0.) status (Count-up is also inhibited.) SIO · Operable · Operable only when the external clock is selected as the shift clock. Note INT Operable

Table 17-1 Standby Mode Status

Note When STOP 0000B is executed, all pins are set to input port mode even if the pins are used in dualfunction mode.

Cautions 1. Always specify a NOP instruction immediately before STOP and HALT instructions.

When an interrupt request flag and the corresponding interrupt enable flag are both set, and the associated interrupt is specified as the standby mode release condition, the system does not enter the standby mode.

#### 17.2 HALT MODE

## 17.2.1 Setting HALT Mode

Executing a HALT instruction sets HALT mode.

Operand b3b2b1b0 of the HALT instruction indicates the HALT mode release conditions.

**Table 17-2 HALT Mode Release Conditions**

Format: HALT b3b2b1b0B

| Bit            | HALT mode release conditionsNote 1                                    |

|----------------|-----------------------------------------------------------------------|

| рз             | When this bit is 1, release by IRQxxx is permitted. Notes 2, 4        |

| b <sub>2</sub> | Fixed at 0                                                            |

| b <sub>1</sub> | When this bit is 1, forced release by IRQTM1 is permitted. Notes 3, 4 |

| b <sub>0</sub> | Fixed at 0                                                            |

**Notes 1.** When HALT 0000B is specified, HALT mode can be released only by reset (RESET input or power-on/power-down reset).

- 2. IPxxx must be 1.

- 3. HALT mode is released regardless of the IPTM status.

- **4.** If a HALT instruction is executed when IRQxxx = 1, the HALT instruction is ignored (treated as a NOP instruction), and HALT mode is not set.

## 17.2.2 Starting Address After HALT Mode is Released

The starting address depends on the release conditions and interrupt enable conditions.

Table 17-3 Starting Address After HALT Mode is Released

| Release condition | Starting address after release                                                                                |

|-------------------|---------------------------------------------------------------------------------------------------------------|

| ResetNote 1       | Address 0                                                                                                     |

| IRQxxxNote 2      | For DI, address subsequent to the HALT instruction                                                            |

|                   | For EI, interrupt vector (When more than one IRQxxx is set, the interrupt vector having the highest priority) |

Notes 1. RESET input and power-on/power-down reset are valid.

2. Except when forced release is made with IRQTM, IPxxx must be 1.

#### 17.3 STOP MODE

## 17.3.1 Setting STOP Mode

Executing a STOP instruction results in STOP mode being set.

Operand b3b2b1b0 of the STOP instruction indicates the STOP mode release conditions.

**Table 17-4 STOP Mode Release Conditions**

Format: STOP b3b2b1b0B

| Bit            | STOP mode release conditionNote 1                              |

|----------------|----------------------------------------------------------------|

| рз             | When this bit is 1, release by IRQxxx is permitted. Notes 2, 3 |

| b <sub>2</sub> | Fixed at 0                                                     |

| b <sub>1</sub> | Fixed at 0                                                     |

| b <sub>0</sub> | Fixed at 0                                                     |

- **Notes 1.** When STOP 0000B is specified, STOP mode can be released only with reset (RESET input or power-on/power-down reset). When STOP 0000B is executed, the microcomputer is initialized to the state existing immediately after the reset.

- 2. IPxxx must be 1. STOP mode cannot be released with IRQTM.

- 3. If the STOP instruction is executed when IRQxxx = 1, the STOP instruction is ignored (treated as a NOP instruction), and STOP mode is not set.

## 17.3.2 Starting Address After STOP Mode is Released

The starting address depends on the release conditions and interrupt enable conditions.

Table 17-5 Starting Address After STOP Mode is Released

| Release condition | Starting address after release                                                                                |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| ResetNote 1       | Address 0                                                                                                     |  |  |  |

| IRQxxxNote 2      | For DI, address subsequent to the STOP instruction                                                            |  |  |  |

|                   | For EI, interrupt vector (When more than one IRQxxx is set, the interrupt vector having the highest priority) |  |  |  |

Notes 1. RESET input and power-on/power-down reset are valid.

2. IPxxx must be 1. STOP mode cannot be released with IRQTM.

## 18. RESET

This product provides three reset functions:

- # Reset by RESET input

- \$ Power-on/power-down reset at power-on or power voltage drop

- % Address stack overflow or underflow reset

# **18.1 RESET FUNCTIONS**

The reset functions are used to initialize device operations. The initialized hardware depends on the reset type. See **Table 18-1** for reset functions.

# **★** Table 18-1 Hardware Statuses after Reset

| Reset type  Hardware              |                 | RESET input during operation Built-in power-on/power-down reset during operation                                      | RESET input in the standby mode Built-in power-on/power-down reset in the standby mode | Stack overflow or underflow                                                                                |

|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Program counter                   |                 | 0000H                                                                                                                 | 0000H                                                                                  | 0000H                                                                                                      |

| Port                              | Input/output    | Input                                                                                                                 | Input                                                                                  | Input                                                                                                      |

|                                   | Output latch    | 0                                                                                                                     | 0                                                                                      | Undefined                                                                                                  |

| General-purpose<br>data memory    | Other than DBF  | Undefined                                                                                                             | Statuses before reset are retained                                                     | Undefined                                                                                                  |

|                                   | DBF             | Undefined                                                                                                             | Undefined                                                                              | Undefined                                                                                                  |

| System register                   | Other than WR   | 0                                                                                                                     | 0                                                                                      | 0                                                                                                          |

|                                   | WR              | Undefined                                                                                                             | Statuses before reset are retained                                                     | Undefined                                                                                                  |

| Control register                  |                 | SP = 5H, IRQTM1 = 1, TMEN = 1, and INT indicate the current status of the INT pin. The others are 0.  See Chapter 10. |                                                                                        | SP = 5H and INT indicate the current status of the INT pin. The others retain their statuses before reset. |

| Timer                             | Count register  | 00H                                                                                                                   | 00H                                                                                    | Undefined                                                                                                  |

|                                   | Modulo register | FFH                                                                                                                   | FFH                                                                                    | FFH                                                                                                        |

| Serial interface shif<br>(SIOSFR) | t register      | Undefined                                                                                                             | Statuses before reset are retained                                                     | Undefined                                                                                                  |

RF: 10H

O O O PDRESEN

Low-voltage detection circuit

Power-on reset circuit

RESET ©

Fig. 18-1 Reset Block Configuration

## 18.2 RESETTING

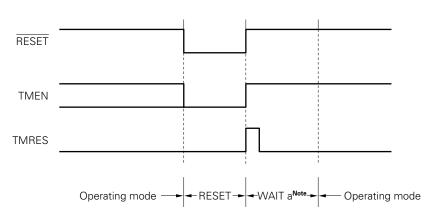

Operation when reset is caused by RESET input is shown in Fig. 18-2.

If the RESET pin is set from low to high, system clock generation starts and an oscillation stability wait occurs with the timer. Program execution starts from address 0000H.

If power-on reset is used, the reset signals shown in Fig. 18-2 are internally generated. Operation is the same as that when reset is caused by RESET input.

At stack overflow and underflow reset, oscillation stability wait time (WAIT a) does not occur. Operation starts from address 0000H after initial statuses are internally set.

Fig. 18-2 Resetting

Note This is oscillation stability wait time. Operating mode is set when the timer counts system clocks  $256 \times 256$  times (approx. 32 ms at fcc = 2 MHz).

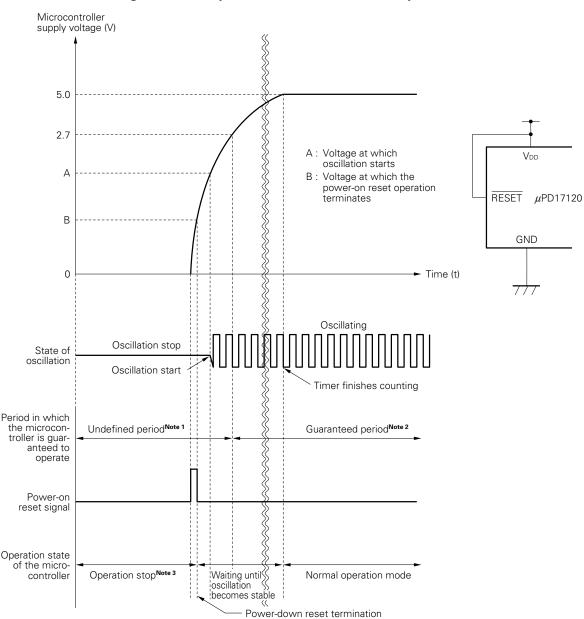

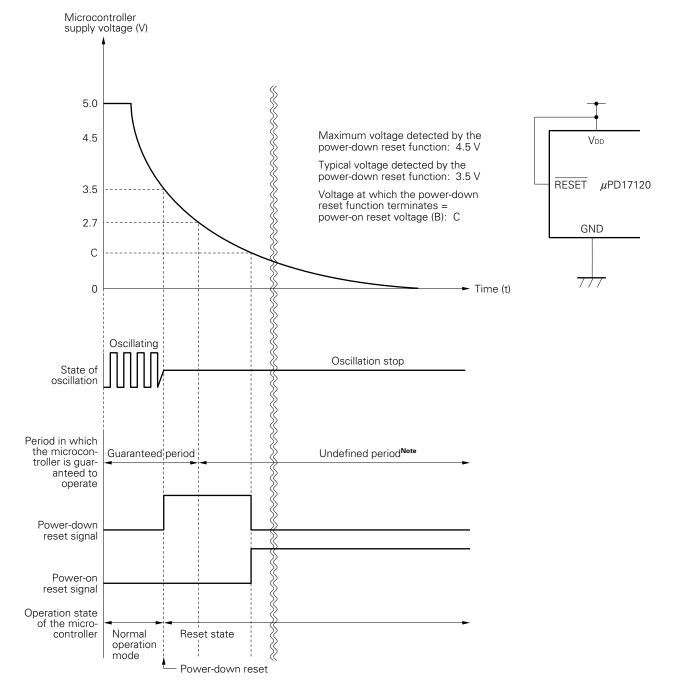

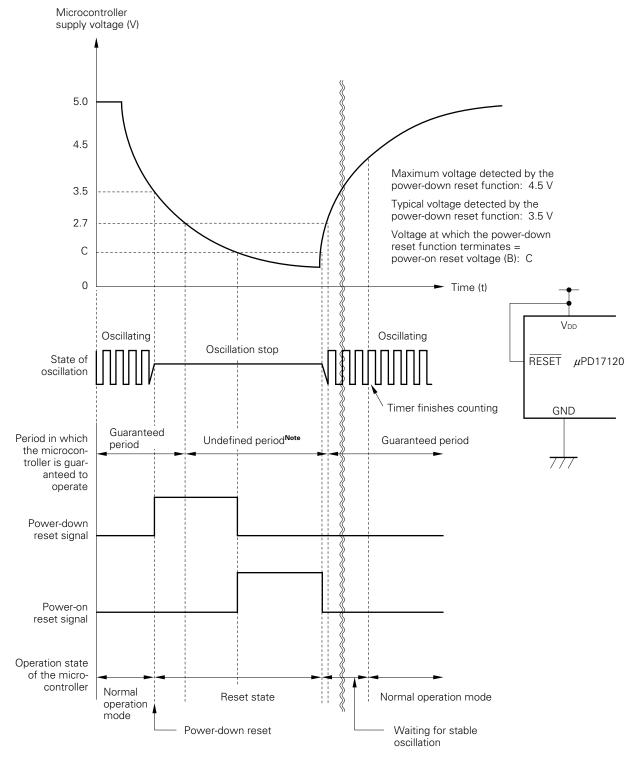

#### 18.3 POWER-ON/POWER-DOWN RESET FUNCTION

The  $\mu$ PD17120 is provided with two reset functions to prevent malfunctions from occurring in the microcontroller. They are the power-on reset function and power-down reset function. The power-on reset function resets the microcontroller when it detects that power was turned on. The power-down reset function resets the microcontroller when it detects drops in the power voltage.

These functions are implemented by the power-voltage monitoring circuit whose operating voltage has a different range than the logic circuits in the microcontroller and the oscillation circuit (which stops oscillation at reset to put the microcontroller in a temporary stop state). Conditions required to enable these functions and their operations will be described next.

★ Caution When designing an application circuit which requires high reliability, do not design a reset function which depends only on a built-in power-on/power-down reset function. Be sure to design a circuit to which an external RESET signal can be input.

## 18.3.1 Conditions Required to Enable the Power-On Reset Function

This function is effective when used together with the power-down reset function.

The following conditions are required to validate the power-on reset function: